# RELIABILITY EVALUATION REPORT

SD4933MR RF DMOS Medium Voltage Technology Transfer in ST Ang Mo Kio (Singapore) Fab

**General Information**

Commercial Product : SD4933MR

**Product Line (Test**

Vehicle)

: 4926

Product Description : DMOS MEDIUM VOLTAGE

Package : M177MR

Silicon Technology : DMOS

**Division** : Power Transistor Division

**Traceability**

**Diffusion Plant** : ST 6" (Singapore)

Assembly Plant : BOUSKOURA (Morocco)

Reliability Assessment

Passed ⊠

Failed

**Disclaimer:** this report is a summary of the qualification plan results performed in good faith by STMicroelectronics to evaluate the electronic devices conformance to its specific mission profile. This report and its contents shall not be disclosed to a third party, except in full, without previous written agreement by STMicroelectronics or under the approval of the author (see below)

#### **REVISION HISTORY**

| Ī | Version | Date            | Author       | Changes description |  |  |

|---|---------|-----------------|--------------|---------------------|--|--|

|   | 1.0     | 21 January 2019 | A.SETTINIERI | Final Report        |  |  |

#### APPROVED BY:

Corrado CAPPELLO ADG Q&R department - Catania ST Microelectronics

#### **TABLE OF CONTENTS**

| 1. | RELI | ABILITY EVALUATION OVERVIEW     | 3 |

|----|------|---------------------------------|---|

|    | 1.1  | OBJECTIVE                       | 3 |

|    |      | RELIABILITY TEST PLAN           |   |

|    | 1.3  | CONCLUSION                      | 3 |

| 2. | DEVI | CE/TEST VEHICLE CHARACTERISTICS | 4 |

|    | 2.1  | GENERALITIES                    | 4 |

|    | 2.2  | PIN CONNECTION                  | 4 |

|    | 2.3  | Traceability                    | 4 |

| 3. | TEST | S RESULTS SUMMARY               | 5 |

|    | 3.1  | LOT INFORMATION                 | 5 |

|    | 32   | TEST RESULTS SUMMARY            | 5 |

Page 3/5

#### 1. RELIABILITY EVALUATION OVERVIEW

#### 1.1 Objective

Reliability evaluation for RF DMOS Medium Voltage technology manufactured in Ang Mo Kio SG6" (Singapore).

#### 1.2 Reliability Test Plan

Reliability tests performed on this device are in agreement with JEDEC and internal spec 0061692 specification and are listed in the Test Plan.

For details on test conditions, generic data used and spec reference see test results summary at Par.3

| # | Stress                                 | Abrv | Reference                                               | Test<br>Flag | Comments |

|---|----------------------------------------|------|---------------------------------------------------------|--------------|----------|

| 1 | Pre and Post-Stress Electrical<br>Test | TEST | User specification or supplier's standard Specification | Y            |          |

| 2 | External Visual                        | EV   | JESD22B-101                                             | Υ            |          |

| 3 | High Temperature Storage Life          | HTSL | JESD22B-101                                             | Y            |          |

| 4 | High Temperature Gate Bias             | HTGB | JESD22A-108                                             | Y            |          |

| 5 | High Temperature Reverse<br>Bias       | HTRB | JESD22A-108                                             | Y            |          |

| 6 | Temperature Cycling                    | TC   | JESD22A-104                                             | Y            |          |

#### 1.3 Conclusion

All reliability preliminary tests have been completed with positive results. Neither functional nor parametric rejects were detected at final electrical testing.

Parameter drift analysis performed on samples submitted to die and package oriented test showed a good stability of the main electrical monitored parameters.

On the basis of the overall results obtained, we can give a positive judgment on the reliability evaluation of the SD4933MR product in RF DMOS MV technology manufactured in Ang Mo Kio SG6" in agreement with JESD047 and ST internal spec 0061692.

Choose an item. **RER Id. N.: 494/2019** Report Template Rev.14

# 2. DEVICE/TEST VEHICLE CHARACTERISTICS

#### 2.1 Generalities

RF DMOS MEDIUM VOLTAGE.

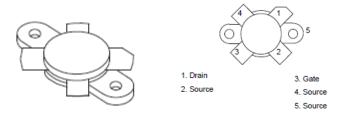

#### 2.2 Pin connection

## 2.3 Traceability

Reference "Product Baseline" document if existing, else provide following chapters/information:

| Wafer fab information                  |                     |  |  |

|----------------------------------------|---------------------|--|--|

| Wafer fab manufacturing location       | SG6                 |  |  |

| Wafer diameter (inches)                | 6"                  |  |  |

| Silicon process technology             | DMOS Medium Voltage |  |  |

| Die finishing front side (passivation) | SiN (nitride)       |  |  |

| Die finishing back side                | Au/As               |  |  |

| Die area (Stepping die size)           | 6220 x 3420 μm      |  |  |

| Metal levels/Materials                 | 1 / AlCu> AlSiCu    |  |  |

| Assembly Information              |                                         |  |  |

|-----------------------------------|-----------------------------------------|--|--|

| Assembly plant location           | BOUSKOURA 2 – (Morocco)                 |  |  |

| Package code description          | M177                                    |  |  |

| Leadframe                         | HEADER D500 4L> HEADER D550 4L NHP FIMo |  |  |

| Die attach material               | Au eutectic                             |  |  |

| Wires bonding materials/diameters | Al-Si / 1.5 mils                        |  |  |

| Encapsulation                     | CAP CERAMIC                             |  |  |

| Reliability Testing Information |                 |  |  |

|---------------------------------|-----------------|--|--|

| Reliability laboratory location | Catania (Italy) |  |  |

| Electrical testing location     | Catania (Italy) |  |  |

Choose an item. RER Id. N.: 494/2019

## 3. TESTS RESULTS SUMMARY

#### 3.1 Lot Information

| Lot# | Commercial Product             | Product lines   | Package  | Wafer Fab | Assembly plant          | Note |  |

|------|--------------------------------|-----------------|----------|-----------|-------------------------|------|--|

|      | SD4933MR                       | 4926            | M177     | SG 6"     | BOUSKOURA (Morocco)     |      |  |

|      | Technology/Product Family data |                 |          |           |                         |      |  |

| 1    | STAC3932F1                     | 4925 double die | STAC244F |           | 66" BOUSKOURA (Morocco) |      |  |

| 2    |                                |                 |          | SG 6"     |                         |      |  |

| 3    | SD3931-10                      | 4925            | M174     |           | BOUSKOUNA (WIDIOCCO)    |      |  |

| 4    |                                |                 |          |           |                         |      |  |

# 3.2 Test results summary

| ш      |                   |    |                       |                                                                          |                      |       |                                | Failure/ | SS    |       |

|--------|-------------------|----|-----------------------|--------------------------------------------------------------------------|----------------------|-------|--------------------------------|----------|-------|-------|

| #      | Stress<br>(Abrv)  | РС | Std ref.              | Conditions                                                               | Sample Size<br>(S.S) | Steps | Lot 1<br>(Double Die)          | Lot 2    | Lot 3 | Lot 4 |

|        | , ,               |    |                       |                                                                          | , ,                  |       | Technology/Product Family data |          |       |       |

| 1      | TEST              |    | User<br>specification | All qualification parts to requirements of the appropriate specification | ropriate device      |       | 320                            | 235      | 235   | 235   |

| 2      | External visual   |    | JESD22<br>B-101       | All devices submitted for testing                                        |                      |       | 320                            | 235      | 235   | 235   |

| Silico | n Oriented Tests  |    |                       |                                                                          |                      |       |                                |          |       |       |

| 3      | HTRB              | N  | JESD22<br>A-108       | Tj=150°C ; BIAS= 200V                                                    | 225                  | 1000H | 0/90                           | 0/45     | 0/45  | 0/45  |

| 4      | HTGB              | N  | JESD22<br>A-108       | Tj=150°C ; BIAS= 20V                                                     | 225                  | 1000H | 0/90                           | 0/45     | 0/45  | 0/45  |

| 5      | HTSL              | N  | JESD22<br>A-101       | Ta= 150°C                                                                | 225                  | 1000H | 0/90                           | 0/45     | 0/45  | 0/45  |

| Packa  | ge Oriented Tests |    |                       |                                                                          |                      |       |                                |          |       |       |

| 6      | тс                | N  | JESD22<br>A-103       | Ta= -65°C / +150°C<br>(1h cycle - 30min at<br>extreme temp.)             | 125                  | 500Cy | 0/50                           | 0/25     | 0/25  | 0/25  |

Choose an item. **RER Id. N.: 494/2019** Report Template Rev.14 **Page 5/5**

# Automotive Discrete Group (ADG) Power Transistor Division

# **Process Change Notification**

### DMOS MV Technology - 4926 Line Transfer in ST's Ang Mo Kio (Singapore) FAB

Dear Customer,

Following the continuous improvement of our service and in order to increase productivity, we announce that *DMOS MV technology - 4926 Line* wafers, currently manufactured in Catania will be performed in ST's Ang Mo Kio (Singapore) FAB.

Wafers produced in Ang Mo Kio (Singapore) FAB, guarantee the same quality and electrical characteristics as per current production.

In the next pages, we are reporting the qualification plan to reach full maturity.

The change has been classified as **Class 1** according to the ST internal rules.

|           | Assessment of impact on Supply Chain regarding following aspects - contractual agreements - technical interface of processability / manufacturability of customer - form, fit, function, quality performance, reliability | Rema<br>risks<br>Sup<br>Cha | s on ply |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------|

| ID        | Type of change                                                                                                                                                                                                            | No                          | Yes      |

| SEM-PW-13 | Move of all or part of wafer fab to a different location/site/subcontractor                                                                                                                                               | Р                           | -        |

P=PCN

The qualification of the change is completed according the qualification plan reported in the following pages; the results are reported in the attached file

Sincerely Yours!

|                                                                                | Tech name  Technology Transfer in ST's Ang Mo Kio (Singapore) FAB                                                                                                                                                             |  |  |  |  |  |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ST Part number:                                                                | ST PNs: DMOS MV4926 Line Package: All the Packages                                                                                                                                                                            |  |  |  |  |  |

| Reason and<br>background of the<br>change                                      | To increase flexibility and increase Capacity                                                                                                                                                                                 |  |  |  |  |  |

| Detailed description<br>of change(s),<br>including affected<br>type of changes | The Diffusion Process and Wafer Testing for <i>DMOS MV4926 Line</i> technology will be performed in ST's Ang Mo Kio (Singapore) FAB.                                                                                          |  |  |  |  |  |

| Impact on form, fit, function, or reliability.                                 | No Impact - No Change                                                                                                                                                                                                         |  |  |  |  |  |

| Datasheet                                                                      | No Impact - No Change                                                                                                                                                                                                         |  |  |  |  |  |

| Benefit of the change                                                          | Capacity and flexibility increase.                                                                                                                                                                                            |  |  |  |  |  |

| Qualification Plan<br>and Implementation<br>date for change                    | 3 Diff. lots – Test vehicle SD4933MR and family data of STAC3932F1 and SD3931-10 The qualification is completed in agreement with JEDEC and internal spec 0061692 specification ( See attached RELIABILITY EVALUATION REPORT) |  |  |  |  |  |

| Traceability<br>Information                                                    | By QA Number                                                                                                                                                                                                                  |  |  |  |  |  |

| PPAP Update                                                                    | NA                                                                                                                                                                                                                            |  |  |  |  |  |